Racyics extends its Silicon Proven ABX Platform Portfolio

Dresden, Germany − February 25, 2019 −

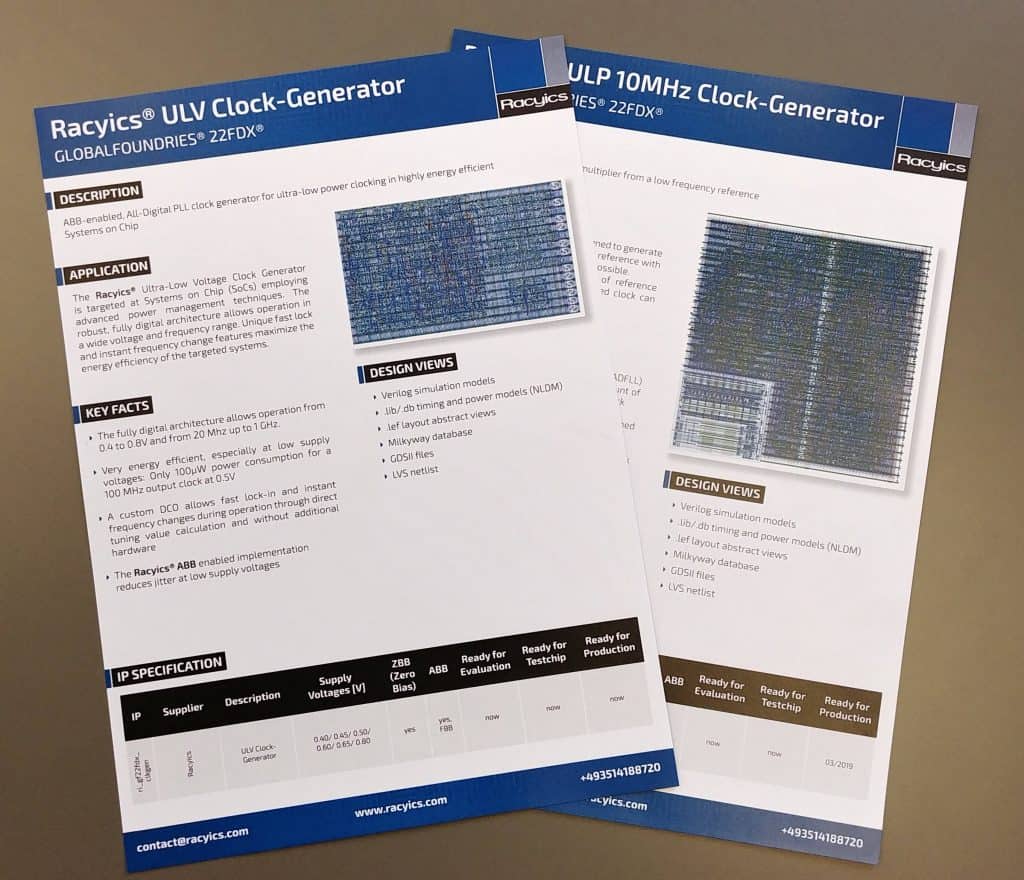

Clock generation is an essential part of every SoC. That’s why Racyics extends its silicon proven, fully Adaptive Body Bias enabled IP offering by adding

- an Ultra-Low-Voltage fast lock-in ADPLL enabled for ABB and DVFS; supply voltage from 0.4V to 0.8V with up to 1 GHz and power consumption as low as 100 µW at 100 MHz; 0.5V operation.

- a 10 MHz, 5µW Ultra-Low-Power ADFLL Clock generator with flexible reference input clock from 32kHz to 1 MHz; suitable for Racyics’ Adaptive Body Bias solution .

Get all the information about our ABX Platform!