# BGA/LGA Package

# IC-Packages for Flip-Chips and Wire-Bonded Chips

## **DESCRIPTION**

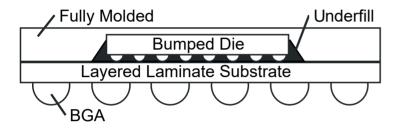

Our packages use fine-pitch layered laminate substrates. On the topside, a single or multiple Flip Chips, Wire-Bonded Chips, or both can be assembled. The bottom side can be equipped with a user-specific LGA or BGA matrix. Thanks to its flexibility, the footprint can also replicate standard packages such as QFN. The entire construction is encapsulated using transfer molding. The figure below illustrates an example of a single-die Flip Chip BGA.

#### **KEY FACTS**

- ▶ Recommended for up to 160 signals (w/o supply pins).

- Mold encapsulation with flat surface for usage in test sockets and pick & place PCB assembly.

- From prototype to series production.

- Multiple test sockets available on the market.

- Laser marking with part serial number

- Multi-die package.

- ▶ SMD passives in package.

## **ELECTRICAL PERFORMANCE**

The following table gives typical resistance, inductance, and capacitance values for the BGA225 package. A detailed SPICE model can be delivered after the design.

| Net Type                                              | R [mΩ]   | L [nH]    | C [pF]   |

|-------------------------------------------------------|----------|-----------|----------|

| Wire-Bonded signal net                                | ~200     | ~1        | ~0.7     |

| Flip-Chip signal net                                  | ~20      | ~0.3      | ~0.5     |

| Wire-Bonded<br>power rail with plane on<br>substrate* | 20 - 200 | 0.1 - 1   | 20 -150  |

| Flip-Chip power rail with plane on substrate          | 1 - 5    | 0.01- 0.1 | 20 - 150 |

<sup>\*</sup>Resistance and Inductance depend highly on the number of wire bonds per rail and wire diameter.

#### **TYPES**

|                    | Pitch   | Pins               | Size                      | Signals<br>(w/o Supply) |

|--------------------|---------|--------------------|---------------------------|-------------------------|

| LGA 64<br>(QFN 64) | 0.5 mm  | 64<br>(Peripheral) | 9 x 9 mm²                 | 50                      |

| LGA 124            | 0.5 mm  | 124<br>(Staggered) | 9 x 9 mm²                 | 85                      |

| BGA/LGA<br>169     | 0.65 mm | 9x9                | 5.5 x 5.5 mm <sup>2</sup> | 135                     |

| BGA/LGA<br>225     | 0.8 mm  | 15x15              | 13 x 13 mm²               | 160                     |

| BGA/LGA<br>324     | 0.8 mm  | 18×18              | 15 x 15 mm <sup>2</sup>   | 200                     |

## **FLIP-CHIP COMPATIBILITY**

Proper placement of bumps is crucial to enable production at medium volumes or for prototypes. Racyics provides working bump patterns based on your requirements.

|                 | Easy    | Standard | Advanced |

|-----------------|---------|----------|----------|

| Bump Diameter   | >70 μm  | >70 μm   | >50 μm   |

| Min. Bump Pitch | >200 µm | >150 µm  | >110 µm  |

## **WIRE-BOND COMPATIBILITY**

Our packages use ball-wedge bonding with gold wire. The bond pad passivation opening should be at least 2.5 times the wire diameter to accommodate the ball size. The minimum length of wires depends on the chip thickness.

|                     | Easy        | Standard    | Advanced    |

|---------------------|-------------|-------------|-------------|

| Wire Diameter       | 25 μm       | 20 µm       | 17.5 µm     |

| Min. Pad<br>Opening | 70 x 70 μm² | 55 x 55 μm² | 44 x 44 μm² |

| Min. Pad Pitch      | 90 µm       | 60 µm       | 51 µm       |

Racyics GmbH