Body biasing is a disruptive 22FDX® feature enabling post silicon adaption of transistor threshold voltages. The Racyics ABX Platform uses Adaptive Body Biasing (ABB) technology to provide reliable and predictable ultra-low voltage (ULV) operation down to 0.4V, compensating process, supply voltage and temperature variations (PVT) to guarantee timing and power with high yield.

For automotive applications, Racyics® ABX RBB enables up to 75% leakage power improvement for automotive grade-1 applications up to 150°C junction temperature.

For ultra-low voltage (ULV) operation, Racyics® ABX FBB enables up to 9X performance at 0.5V.

Key Facts

- Comprehensive ABX platform for ULP and high-performance applications

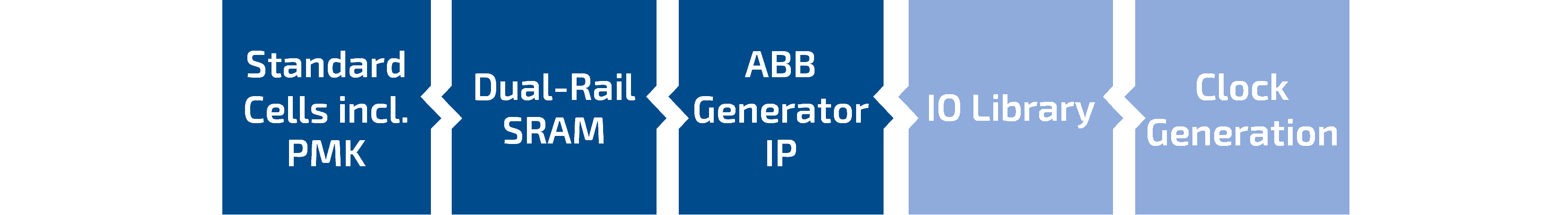

- ABB generator, standard cells, SRAM IP available

- 75% leakage reduction (at Automotive Grade-1 at 150°C and 0.8V) with Racyics ABX® RBB

- Up to 9X performance with Racyics ABX® FBB (versus no-bias)

- Corner tightening and ABB-aware implementation for improved PPA

- Guaranteed performance and power

- Easy-to use turnkey ABB solution based on standard design flow and sign-off

- Transparent ABX® inferred Power-Performance-Area (PPA) improvement at design time

- Silicon-proven

- Free evaluation kit via sales@racyics.com available now!

Product Sheets

| ABX Platform | Racyics ABX Platfom › |

| ABX enabled Standard Cell Libraries incl. PMK | Racyics ABX Standard Cell Libs |

| ABX enabled Dual Rail SRAM | Racyics ABX Dual Rail SRAM › |

| ABX enabled Single Rail SRAM | Racyics ABX Single Rail SRAM › |

|

ABB Generator IP for ABX Platform

|

|

| IO Library* | Racyics IO Library › |

| ULV Clock Generator 20 Mhz up to 1 GHz (ADPLL)* | Racyics ULV Clock Generator 20MHz to 1GHz › |

| ULP 10 MHz Reference Clock Generator (ADFLL)* | Racyics ULP 10MHz Clock Generator › |

| ULP 2 GHz Reference Clock Generator (ADPLL)* | Racyics ULP 2GHz Clock Generator › |

| ULP Power and Clock Generation IP* | Racyics ULP Power and Clock Generation› |

| Voltage and Temperature Sensor* | Racyics Voltage and Temperature Sensor› |

| Crystal oscillator designed to work with 32 kHz crystal* | Racyics Crystal oscillator designed to work with 32 kHz crystal› |

| Universal Chiplet Interconnect Express (UCIe) PHY | Racyics Universal Chiplet Interconnect Express (UCIe) PHY› |

| IP Catalog Sheet | Racyics IP Catalog Sheet› |

| * Additional IP for glue-less interfacing to ULV Racyics® ABX Platform | |